The Future of Weak Memory 2024

# A case against semantic dependencies

### **Ori Lahav, Tel Aviv University**

Based on joint discussions with Minki Cho, Chung-Kil Hur, Sung-Hwan Lee, Ben Simner

Imagine a new model for  $C/C_{++}$  that works in three steps:

- <u>Step 1:</u> "calculate" a set S of candidate program execution graphs

- <u>Step 2: given S, derive semantic dependency</u> (sdep) for each graph

- <u>Step 3:</u> apply the consistency predicate from the C/C++ standard

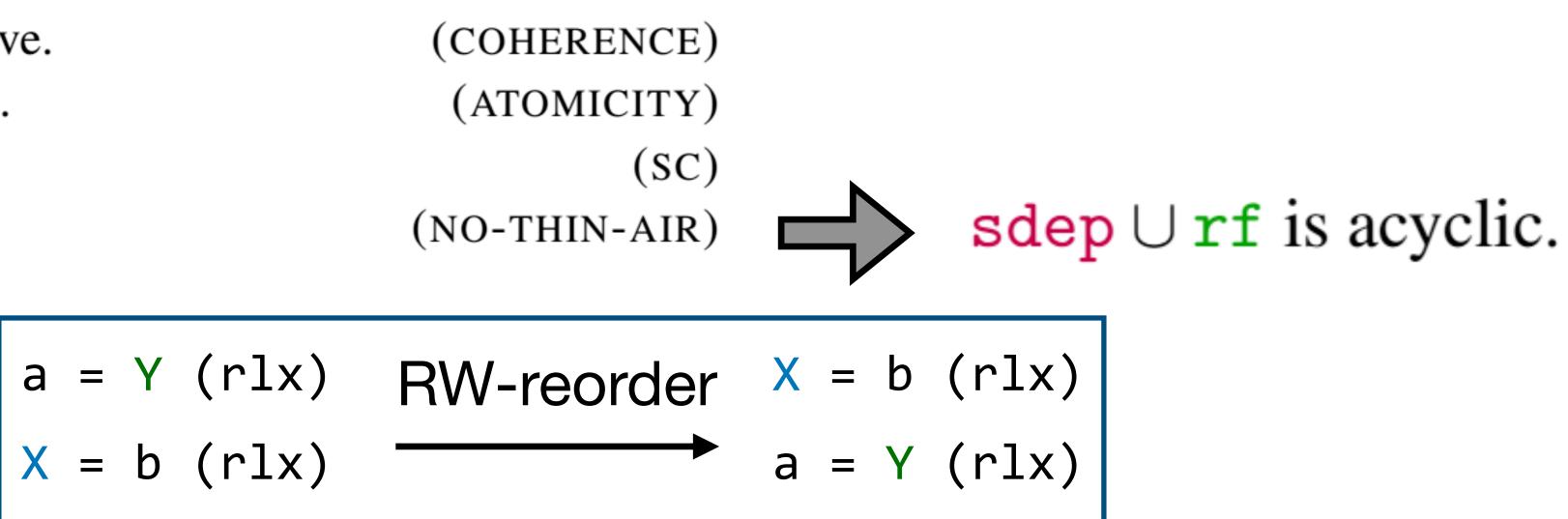

**Definition 1.** An execution G is called RC11-consistent if it is complete and the following hold:

- hb; eco? is irreflexive.

- $\operatorname{rmw} \cap (\operatorname{rb}; \operatorname{mo}) = \emptyset$ .

- psc is acyclic.

- $po \cup rf$  is acyclic.

X = b (rlx)

Imagine a new model for  $C/C_{++}$  that works in three steps:

- <u>Step 2: given S, derive semantic dependency</u> (sdep) for each graph

- <u>Step 3:</u> apply the **consistency predicate** from the C/C++ standard

- I believe this approach can't work. I argue via example that:

- Step 2 cannot be thread-local

- Step 2 has to be aware of the consistency predicate in step 3

### • <u>Step 1:</u> "calculate" a set S of candidate program execution graphs

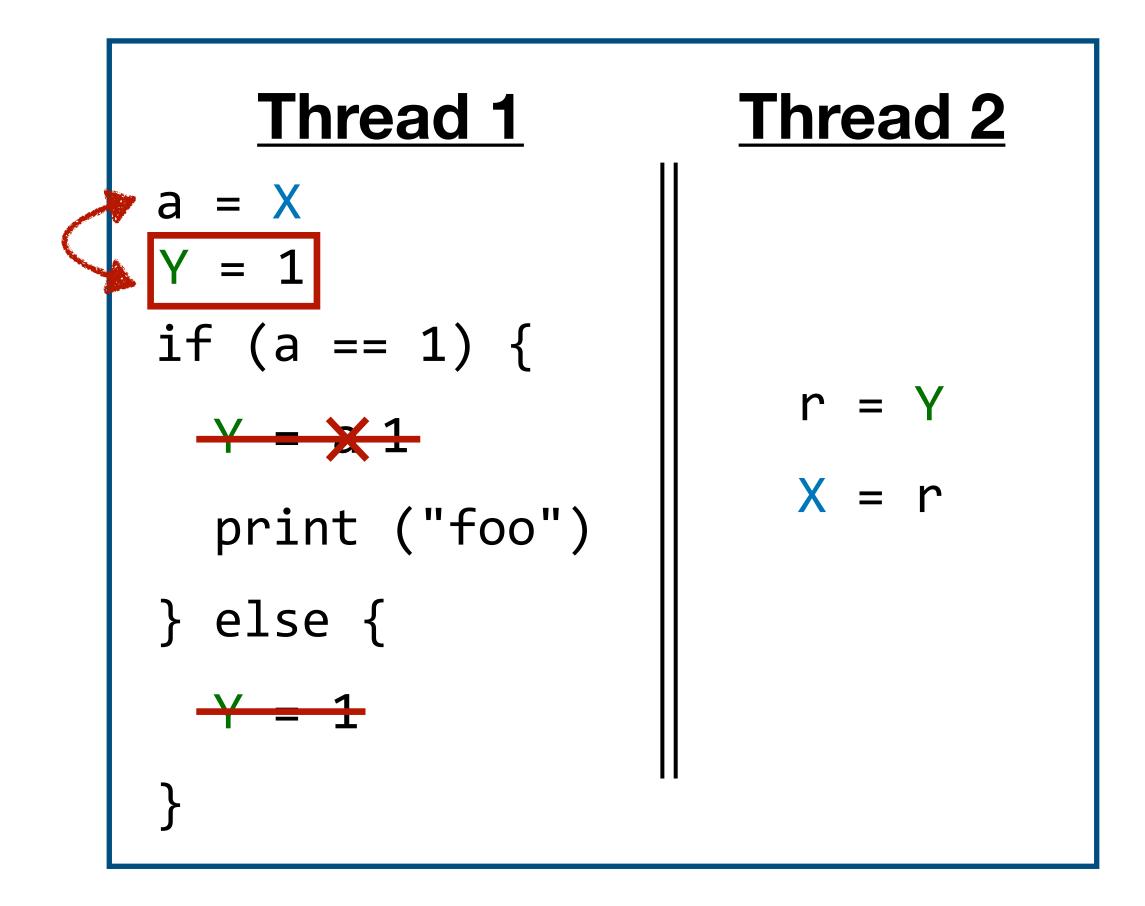

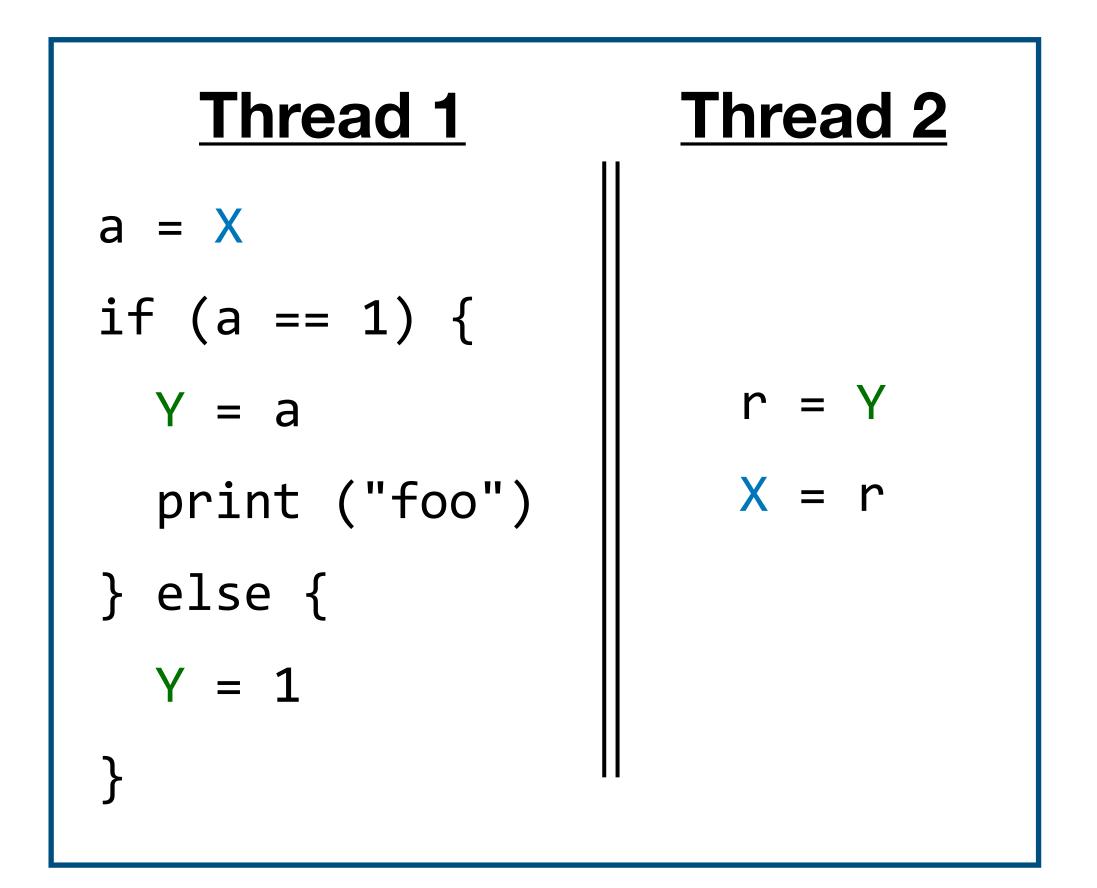

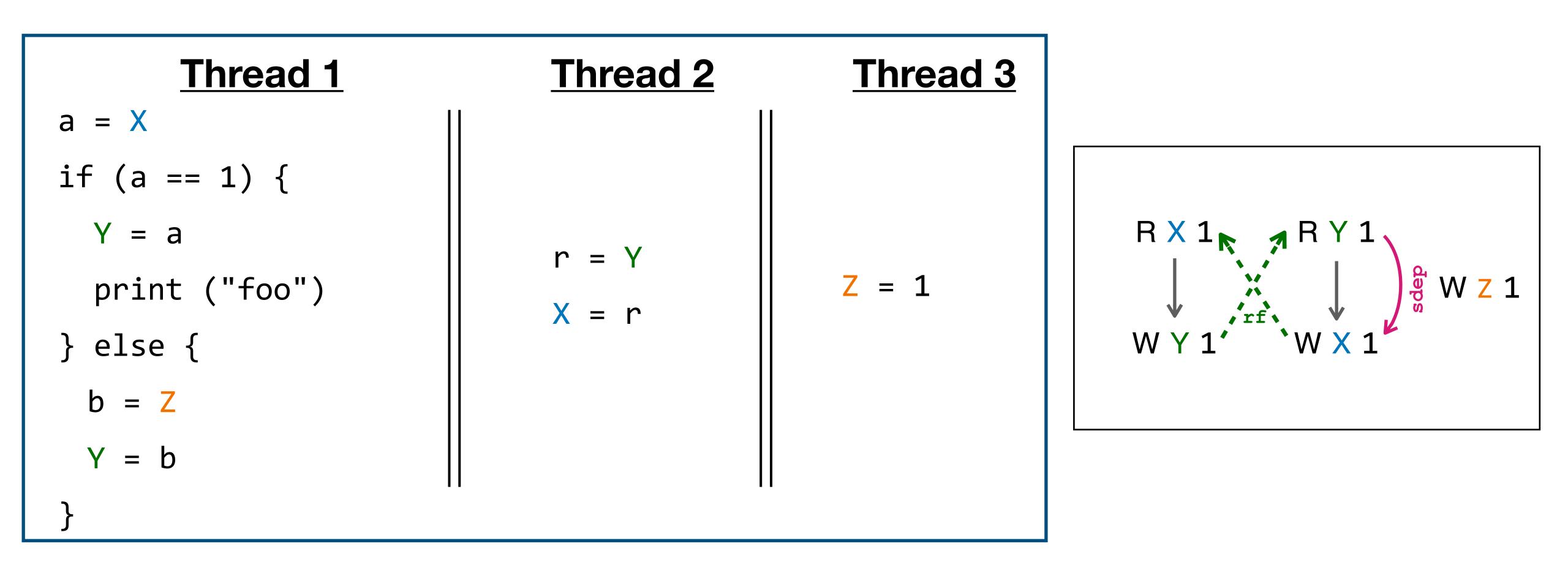

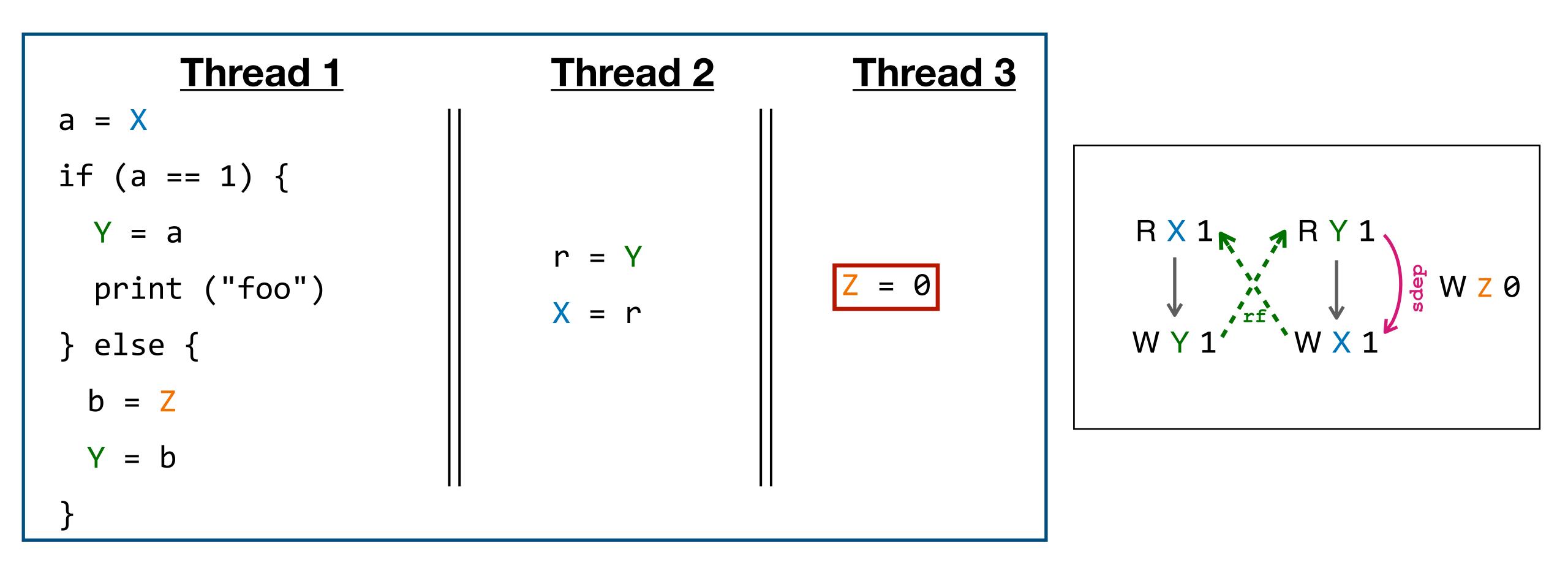

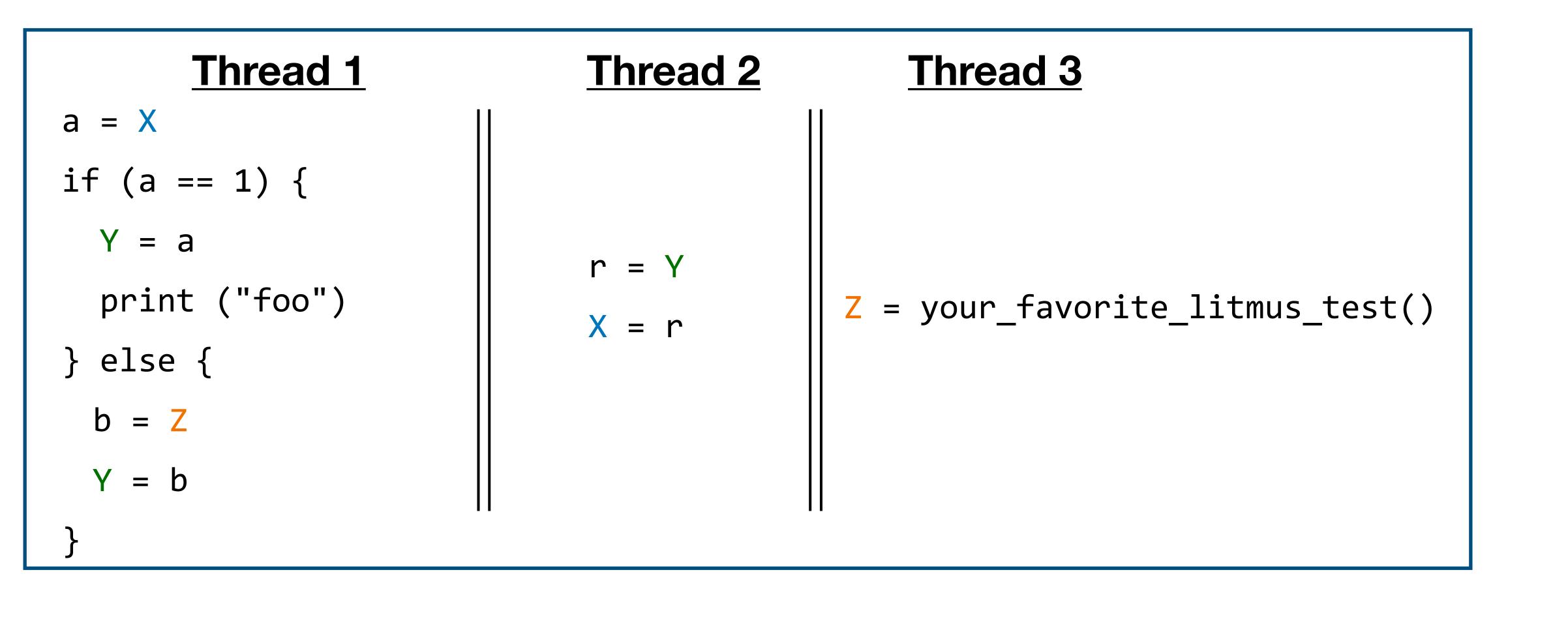

## Can "foo" be printed?

### sdep approach

## Main example

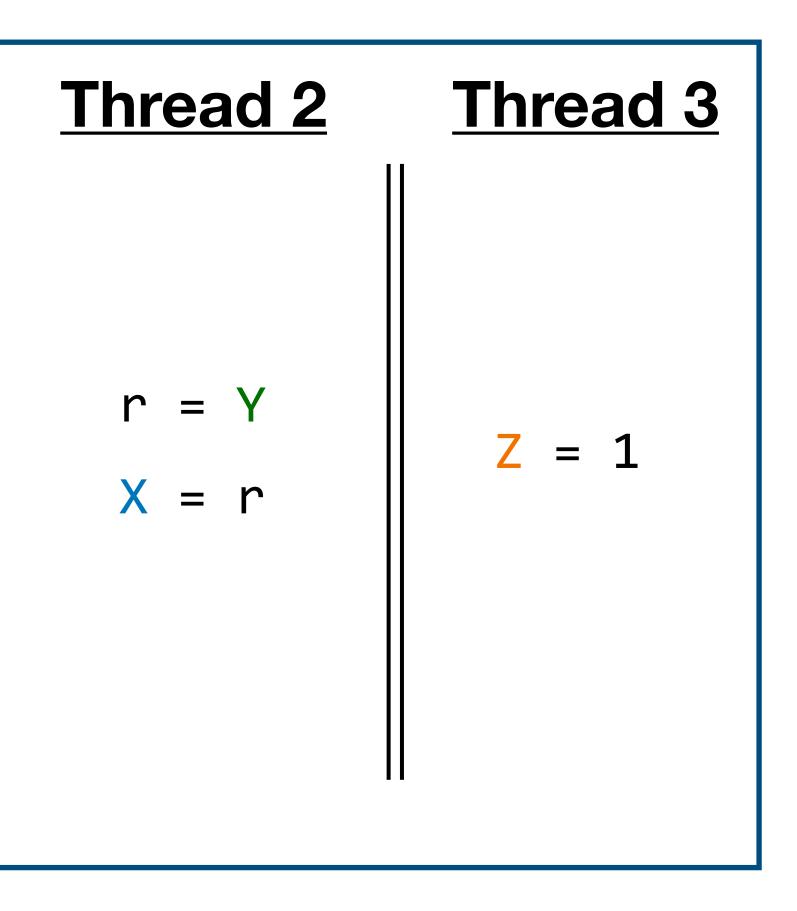

Thread 1 = X а if (a == 1) { Y = aprint ("foo") } else { b = ZY = b

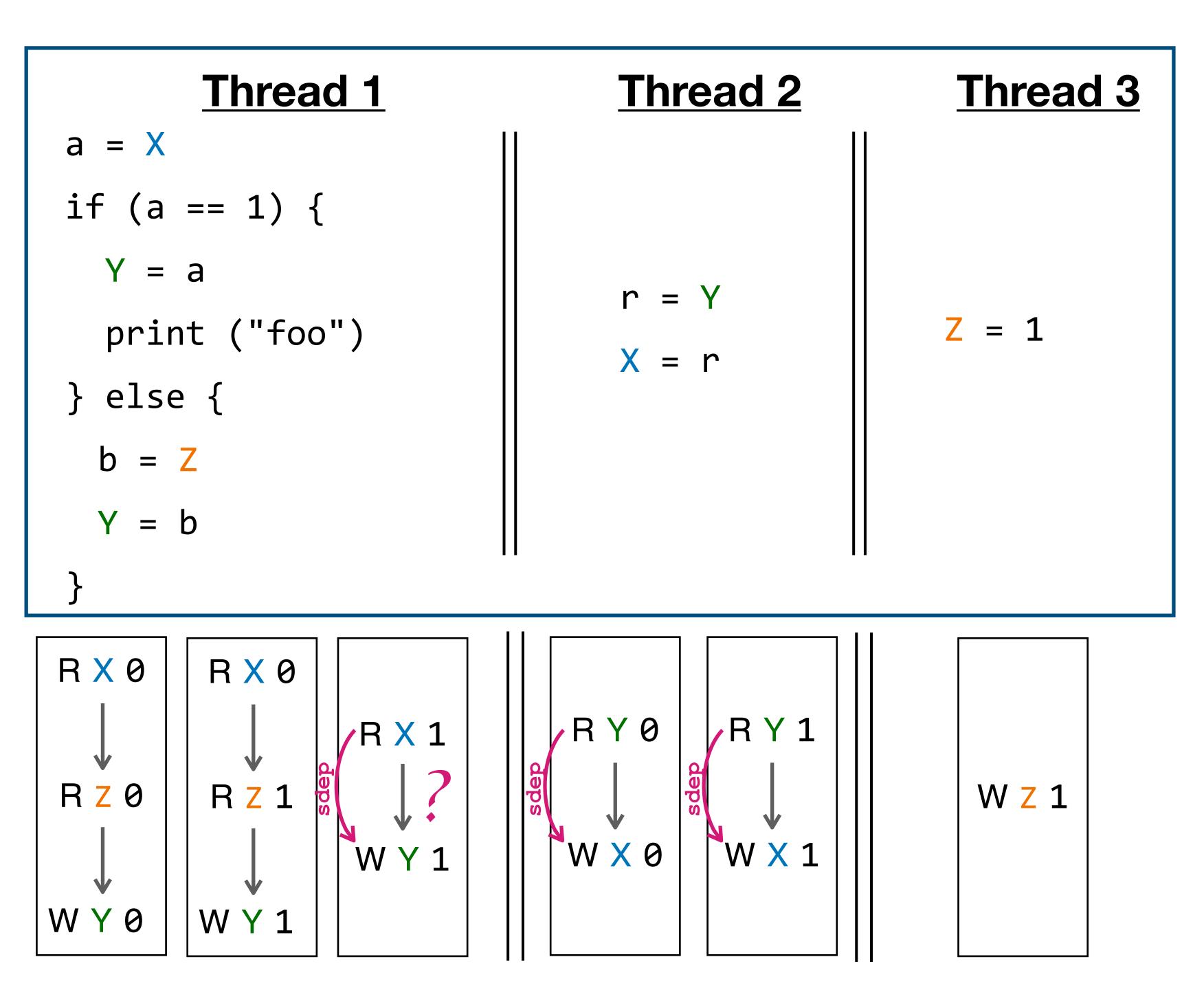

R X 1 <sub>▶</sub> 🖪 R Y 1 g WZ1 , rf. W Y 1

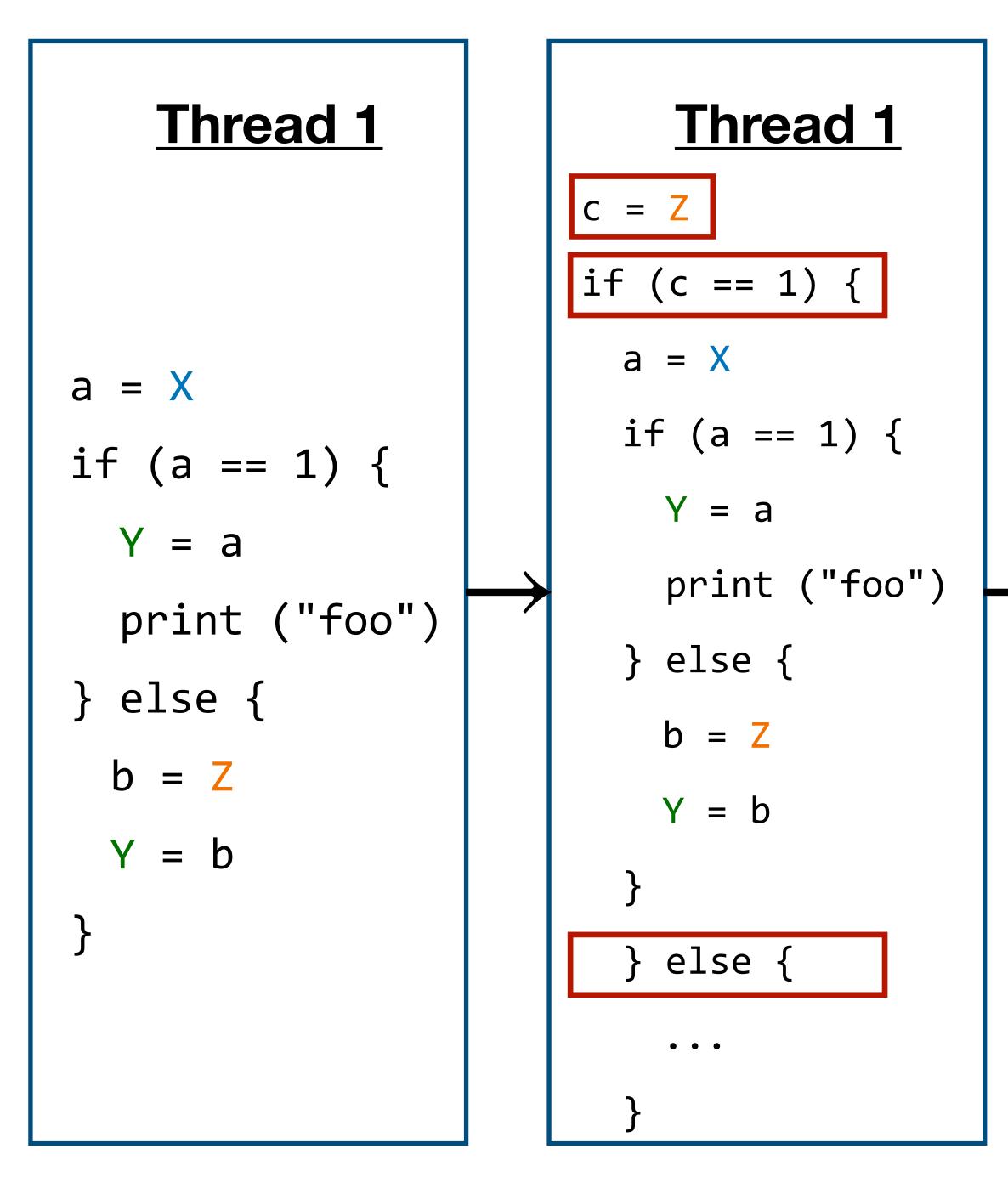

- Printing "foo" has to be allowed, assuming we allow compilers to:

- Introduce redundant loads

- Forward load across atomics:

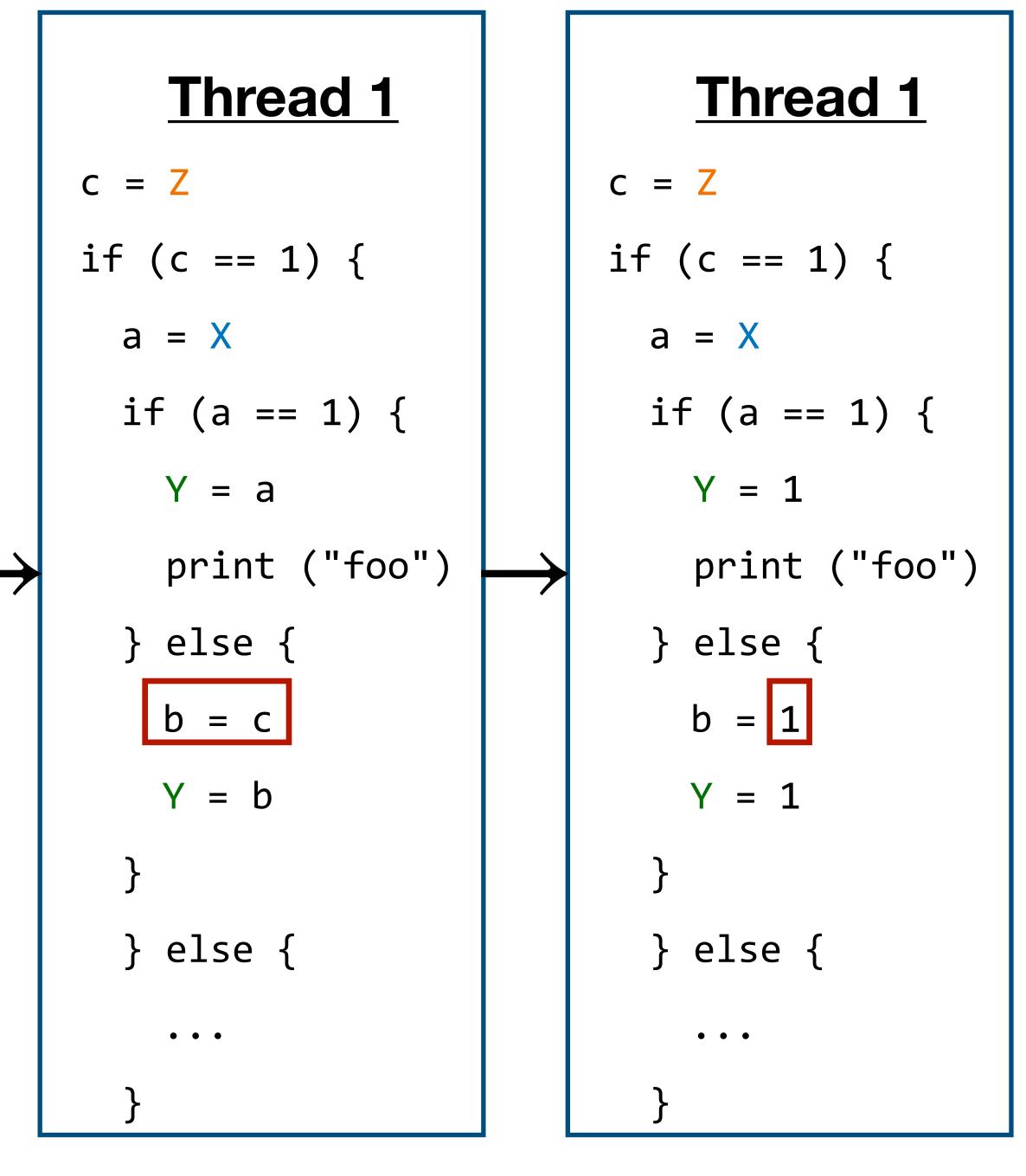

$c = Z; a = X; b = Z \rightarrow c = Z; a = X; b = c$

Both are performed by LLVM/GCC on non-atomics (Z can be easily made non-atomic)

- Printing "foo" has to be allowed, assuming we allow compilers to:

- Introduce redundant loads

- Forward load across atomics:

$c = Z; a = X; b = Z \rightarrow c = Z; a = X; b = c$

Both are performed by LLVM/GCC on non-atomics (Z can be easily made non-atomic)

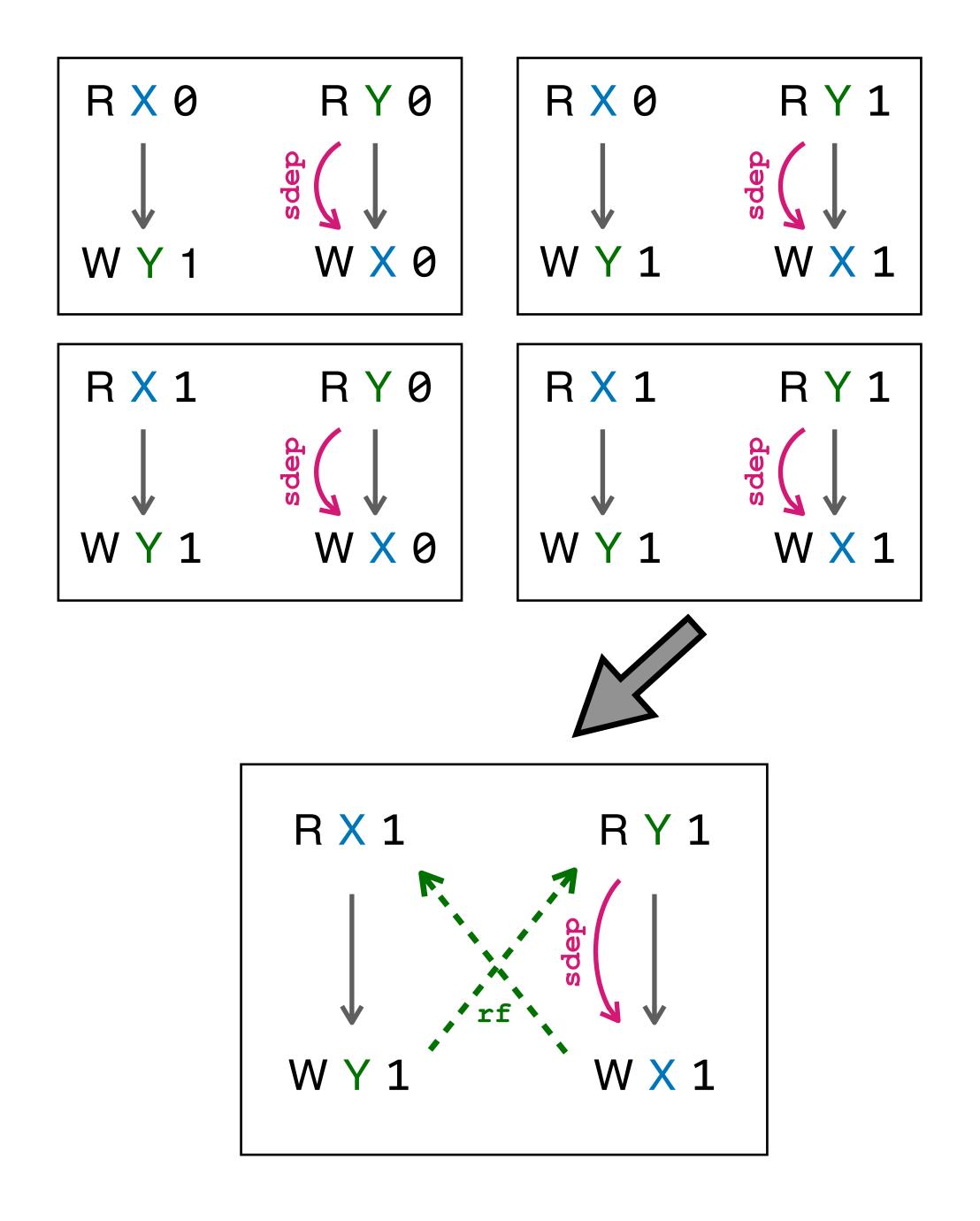

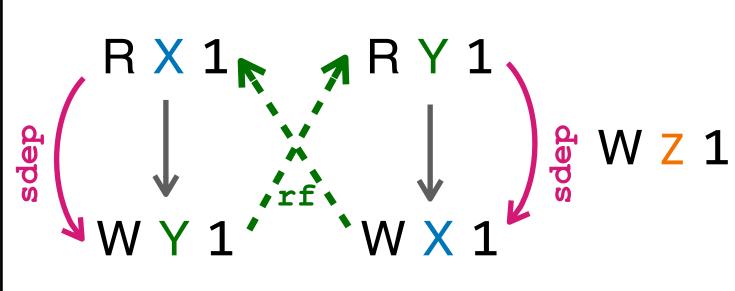

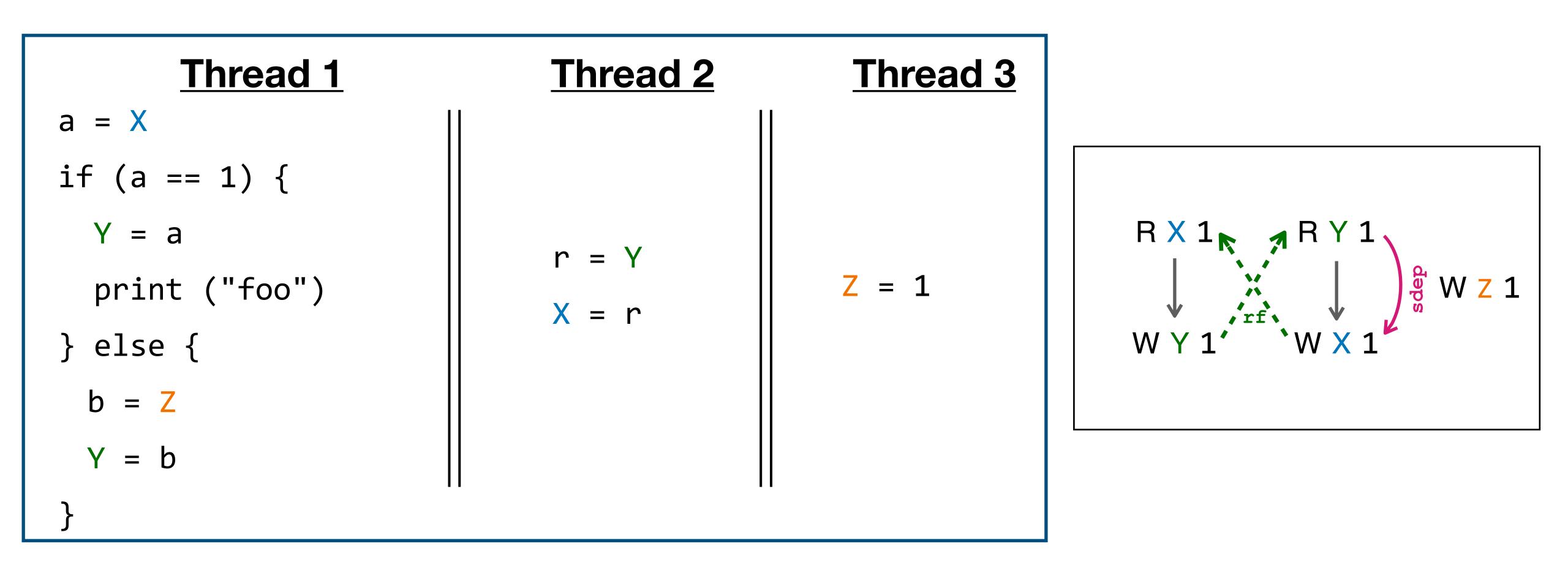

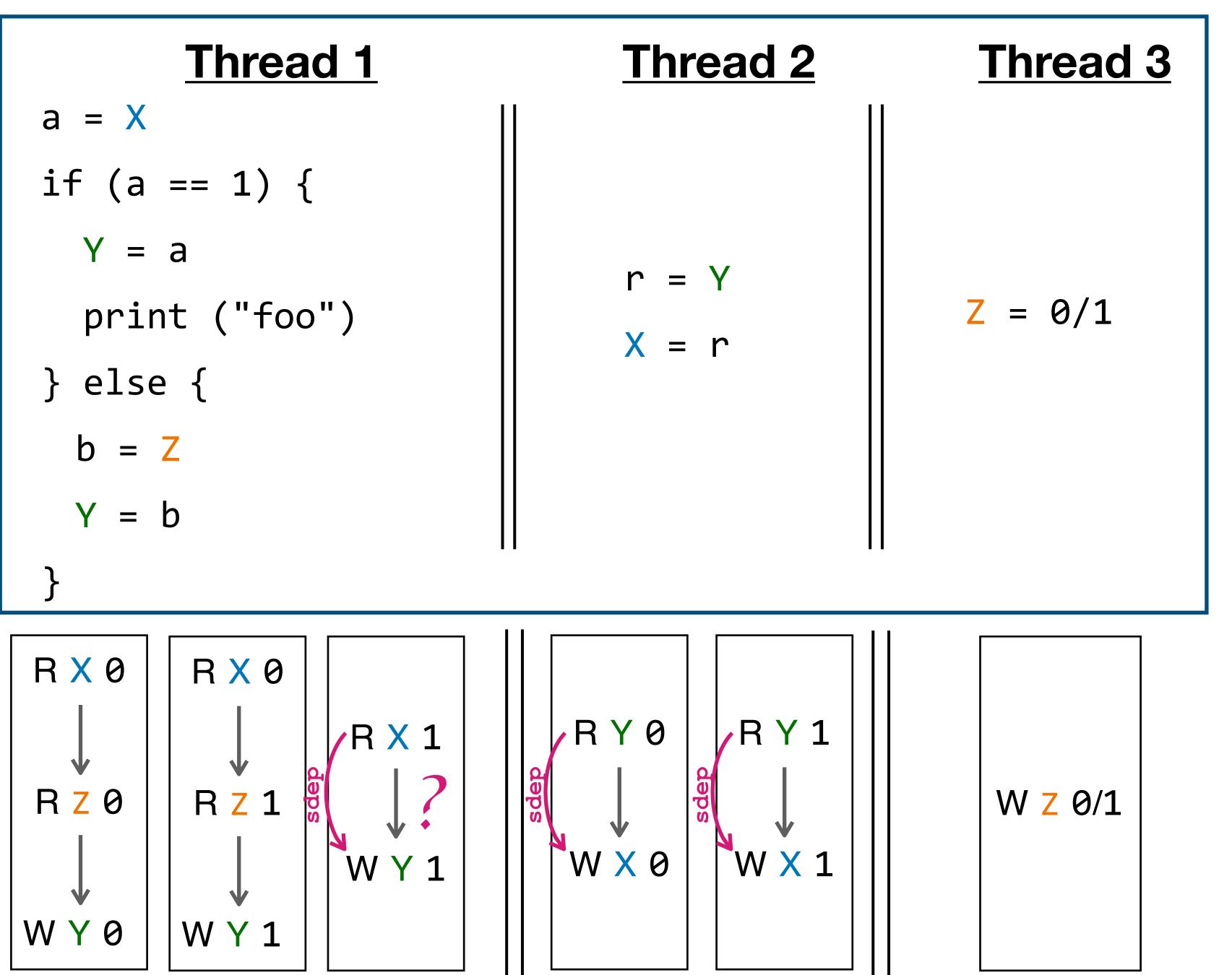

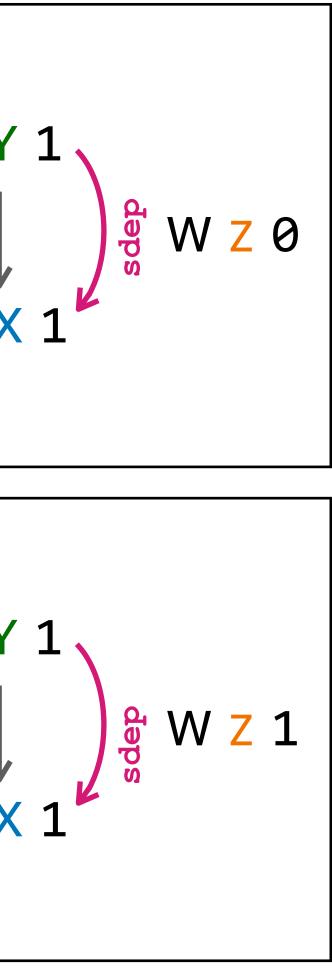

• With new Thread 3, printing "foo" has to be disallowed (thin-air!)

R X 1 💦 🖪 R Y 1 **b** Z W 20 W Y 1 📌 R Y 1 R X 1

WX1

Step 2 (sdep calculation) cannot be thread local!

sdep

₩WY1

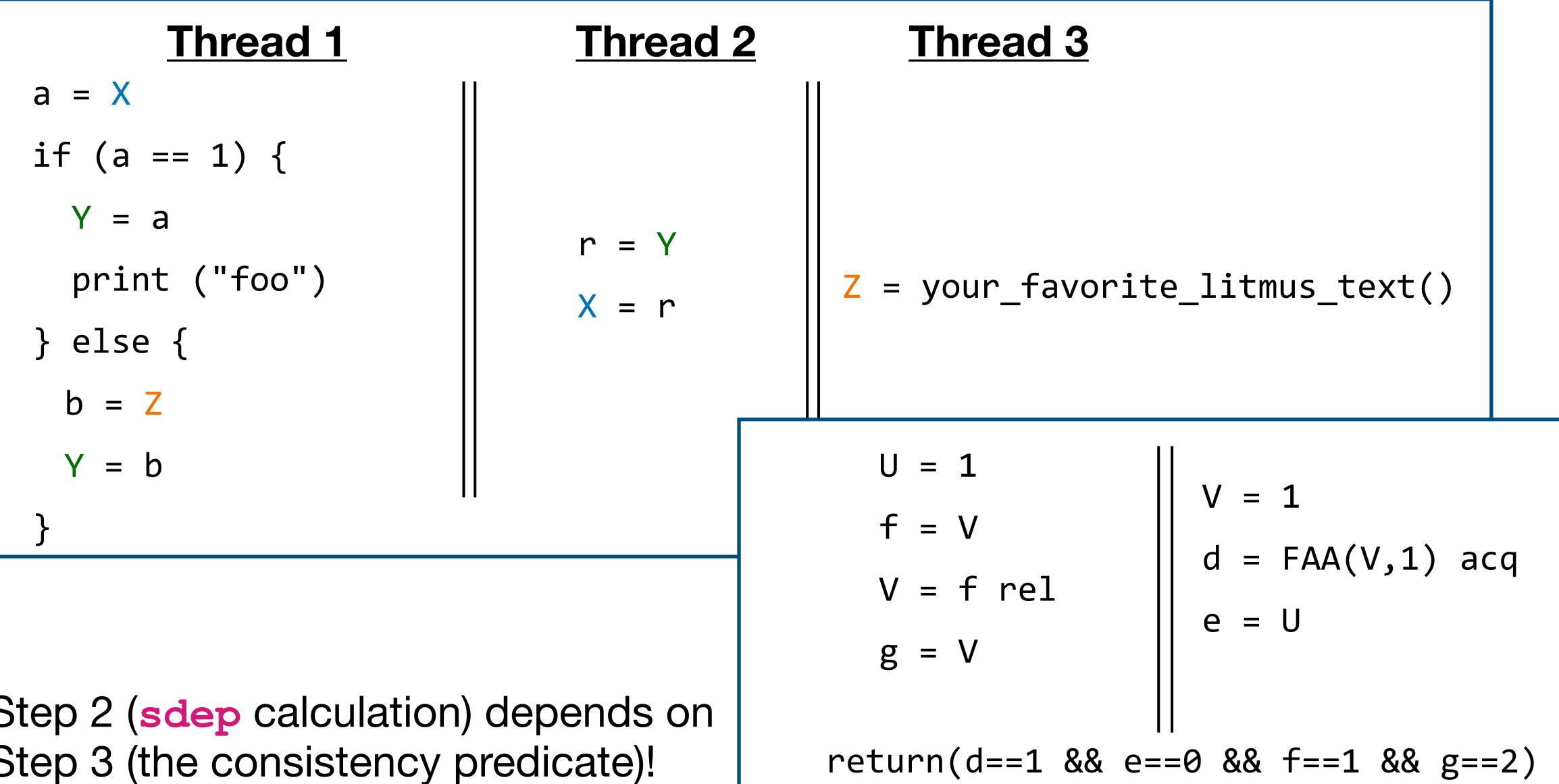

Step 2 (sdep calculation) depends on Step 3 (the consistency predicate)!

### <u>Substitution of Equivalents</u> — "sanity condition" for weak memory models:

equivalent in M (assuming f() uses a disjoint set of locations wrt rest of the program).

• If f() always returns  $\theta$  in a memory model M, then f() and  $\theta$  should be a

## **Reasoning-aware sdep?**:(

- sdep calculation has to take intro account our reasoning principles.

- No thin air values: f() never returns 1 in some (possibly inconsistent) execution  $\implies$  sdep must exist

- A new (sound) program logic can prove that f() never returns 1  $\implies$  sdep must exist

- We have a memory model for reasoning (weaker than the "real" model).

- For reasoning to be potentially precise, sdep needs take into account the full consistency predicate.

# The source of the problem

- Semantic dependencies are "dynamic" rather than "static":

- program point.

- such dynamic dependencies.

The approach we discussed fails to do so.

•  $sdep \iff$  the model allows a thread to read some value at a certain

Event-structure-based / pomset models / "Promising Semantics" capture

(MACHINE: NORMAL)

$$\langle \mathcal{T}(\tau), P_G, M \rangle \rightarrow^+ \langle T', P_G', M' \rangle$$

$\langle T', P_G', M' \rangle \rightarrow^* \langle \langle \_, \_, \emptyset \rangle, \_, \_ \rangle$

$\langle \mathcal{T}, P_G, M \rangle \rightarrow \langle \mathcal{T}[\tau \mapsto T'], P_G', M' \rangle$

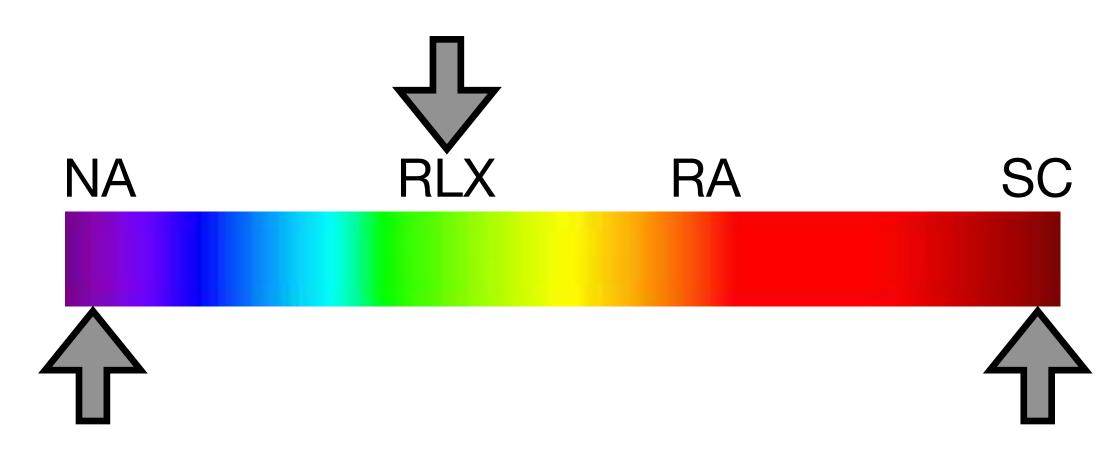

# A fresh look on the out-of-thin-air problem

- The discussion about the OOTA problem in  $C/C_{++}$  revolves around memory order relaxed

- Is it indeed expensive to forbid RW reordering of relaxed accesses?

- More provocatively: do we really need relaxed writes?

- A (more practical?) challenging problem arises with:

- Strong accesses (SC) or mutexes that allow races

- Weak accesses (non-atomic) that allow optimizations, including load introduction

see our PLDI'23 paper