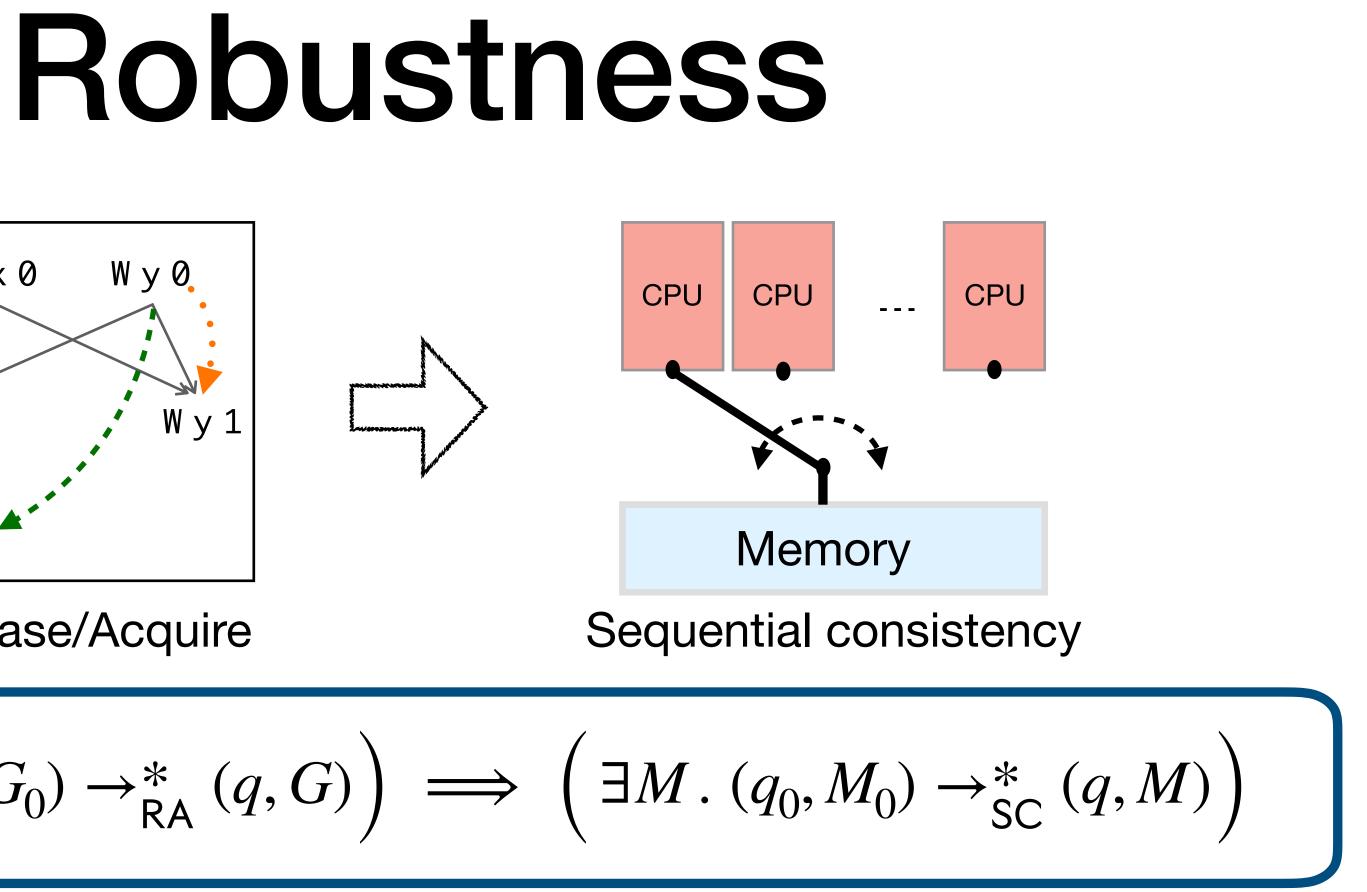

### Robustness Against Release/Acquire Semantics

Ori Lahav

Roy Margalit

### A short story: Peterson's algorithm in C++

- In 1981, Peterson proposed a simple algorithm for critical section in shared memory.

- It assumes sequential consistent shared memory (SC).

• Q: How to implement Peterson's algorithm in C/C++11?

## **A short story:** *Peterson's algorithm in C++*

```

Peterson::Peterson() {

__victim.store(0, memory_order_release);

__interested[0].store(false, memory_order_release);

__interested[1].store(false, memory_order_release);

}

void Peterson::lock() {

int me = threadID; // either 0 or 1

int he = 1 - me; // the other thread

__interested[me].exchange(true, memory_order_acq_rel);

__victim.store(me, memory_order_release);

while (__interested[he].load(memory_order_acquire)

&& _victim.load(memory_order_acquire) == me)

continue; // spin

```

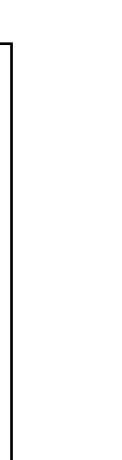

C++ atomics and memory ordering, blog post by **Bartosz Milewski** <u>https://bartoszmilewski.com/2008/12/01/c-atomics-and-memory-ordering/</u>

- A subsequent post by Anthony Williams analyzed both algorithms:

- Bartosz's implementation is indeed wrong.

- Dmitriy's implementation is *correct*.

https://www.justsoftwaresolutions.co.uk/threading/petersons\_lock\_with\_C++0x\_atomics.html

"Any time you deviate from SC, you increase the complexity of the problem by orders of magnitude."

A short story: Peterson's algorithm in C++

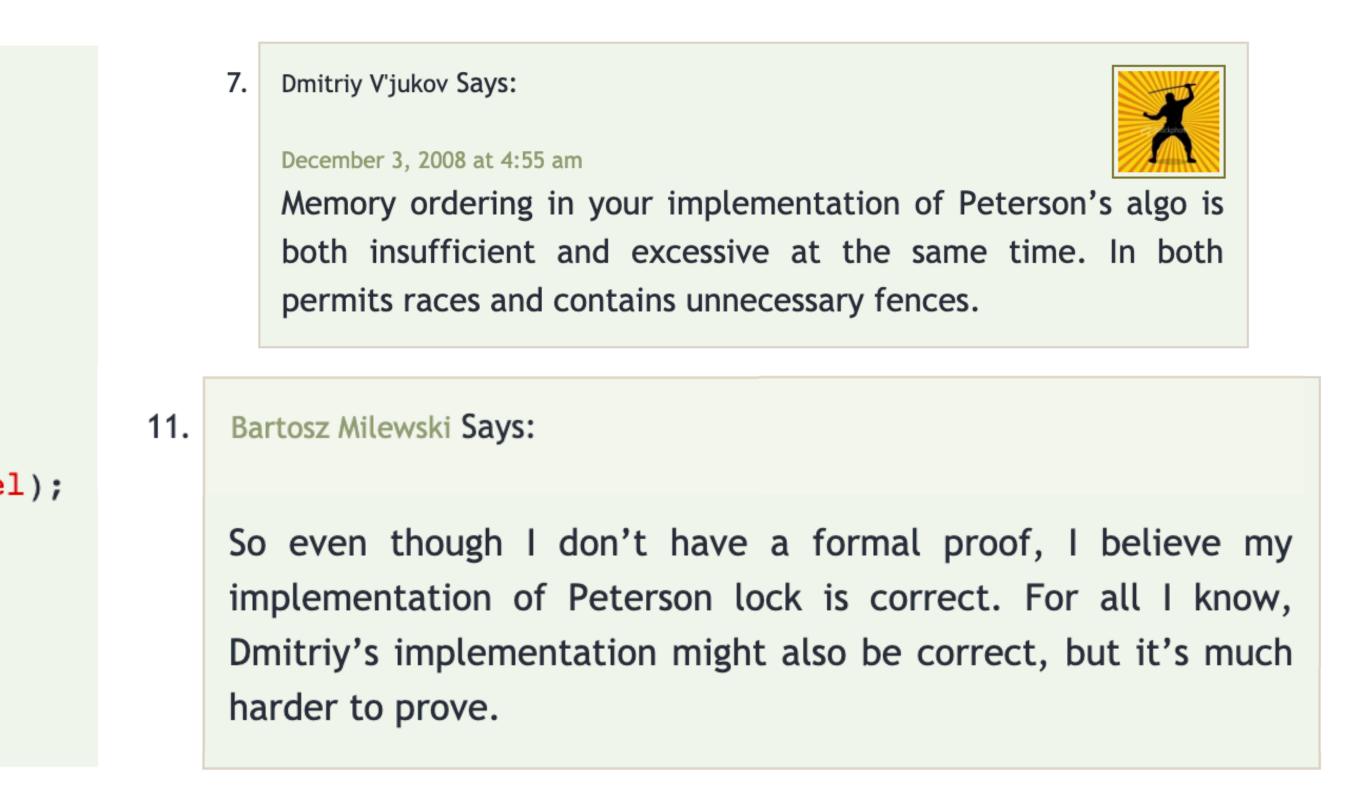

| verification<br>under<br>weak memory |  | verification under<br>sequential<br>consistency | + | robustness |

|--------------------------------------|--|-------------------------------------------------|---|------------|

|--------------------------------------|--|-------------------------------------------------|---|------------|

- Key ingredient in automatic fence insertion

- Our focus: C/C++11's **Release/Acquire** fragment

- Previous work: hardware models (especially **x86-TSO**)

### Goal

Automatically establish robustness of programs against a weak memory model

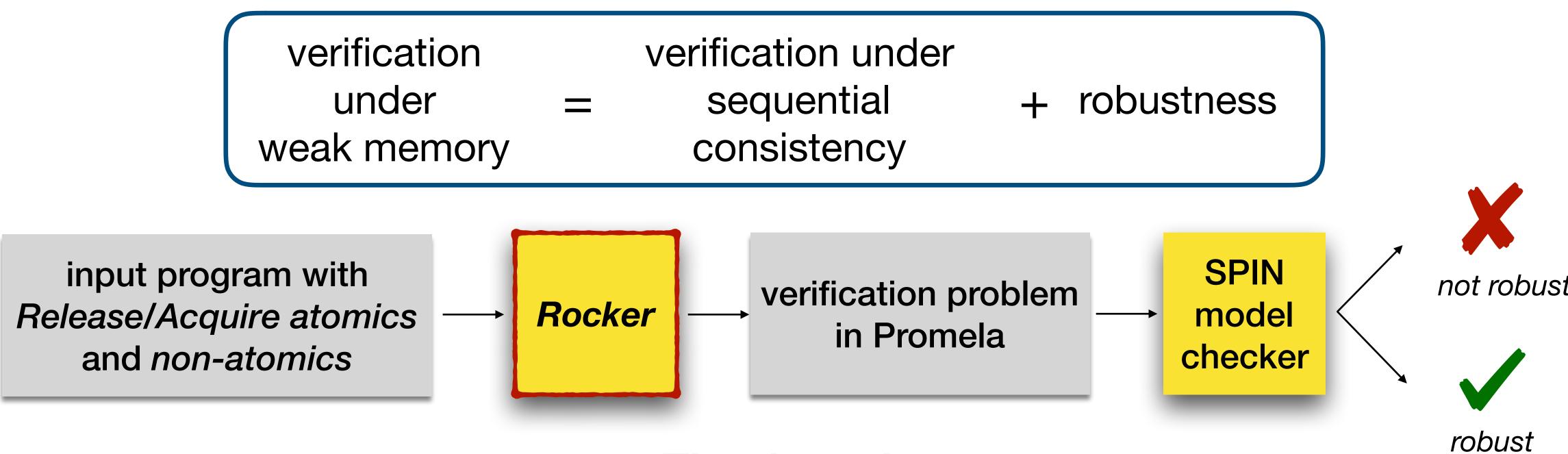

## **Our Contribution**

### Theorem

Execution-graph robustness against Release/Acquire is decidable and **PSPACE-complete**.

- as verification under SC

- A tool for verifying execution-graph robustness

input program with Rocker **Release/Acquire atomics** and *non-atomics*

**Evaluation** on several challenging synchronization algorithms

as robustness against x86-TSO

robust

## Release/Acquire in C/C++11

**Implementability**

- allows cheaper implementation (w.r.t. SC):

- **x86-TSO**: use primitive accesses

- IBM Power: use "lightweight" fences

### Programmability

- ensures the DRF property

- often *sufficiently strong*:

- but not always...

(e.g., Perterson's algorithm)

- supports "message passing" idiom

### atomic store explicit(&x, r, memory\_order\_release)

- r = atomic **load** explicit(&x, **memory\_order\_acquire**)

- atomic fetch\_add explicit(&x, r, memory\_order\_acq\_rel)

- b = atomic compare exchange strong explicit(&x, &r1, r2, memory order acq rel, memory order acquire)

- atomic thread **fence**(memory\_order\_seq\_cst)

### Syntax

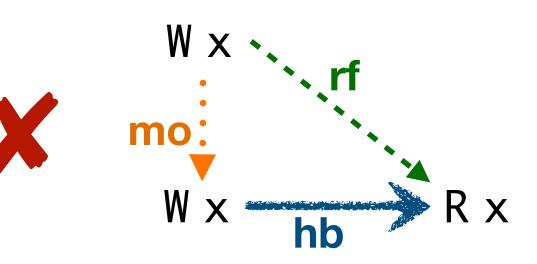

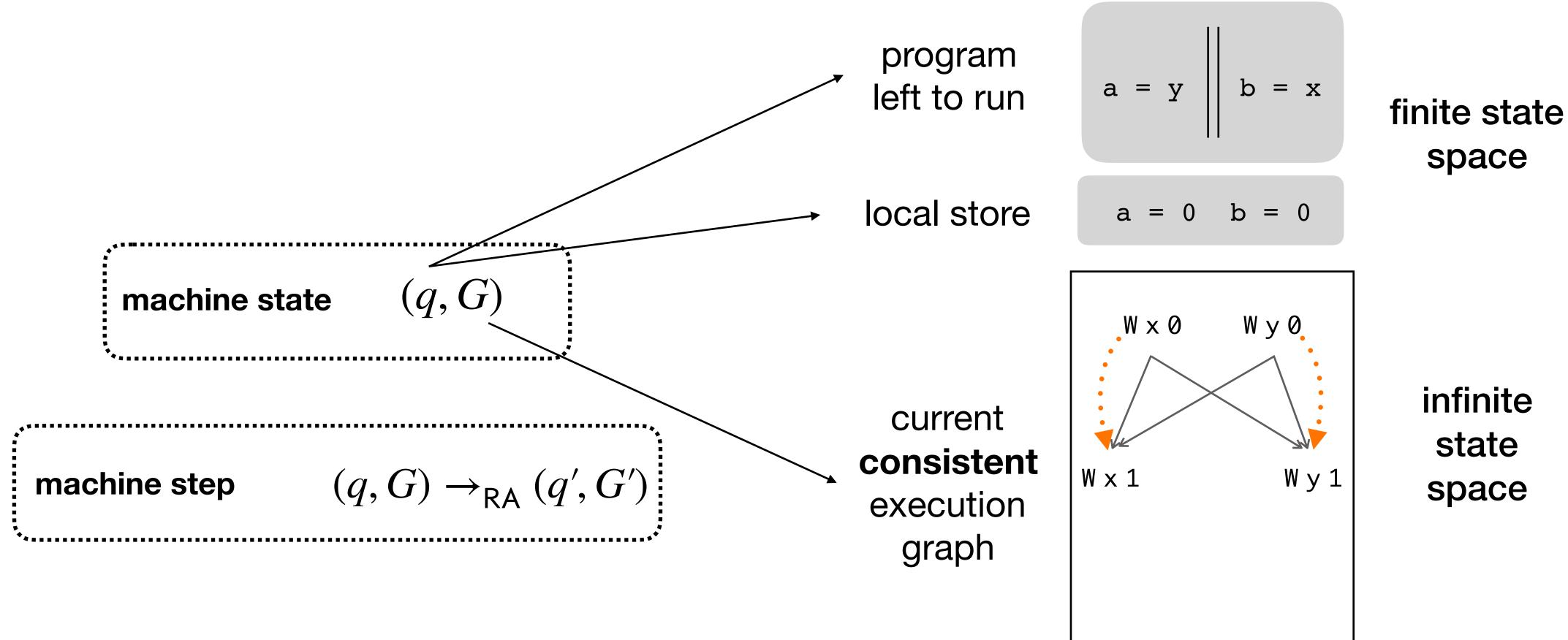

### Semantics (one-slide course)

- A form of *causal consistency*

- Defined declaratively using execution graphs

happens-before =

(program-order ∪ reads-from)<sup>+</sup>

modification-order - total order on writes to the same location

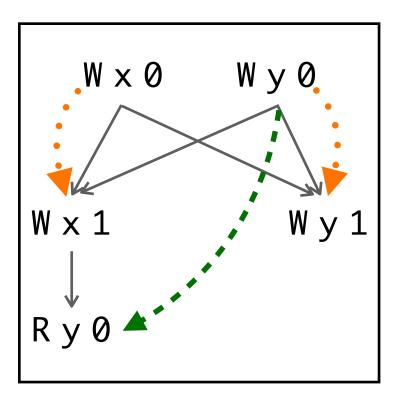

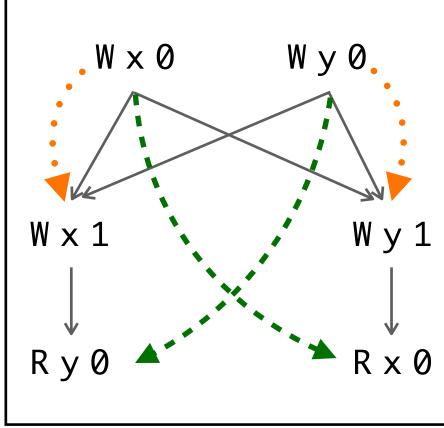

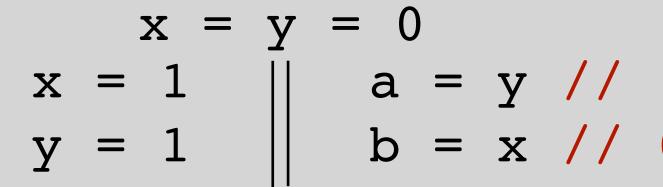

Message passing litmus test

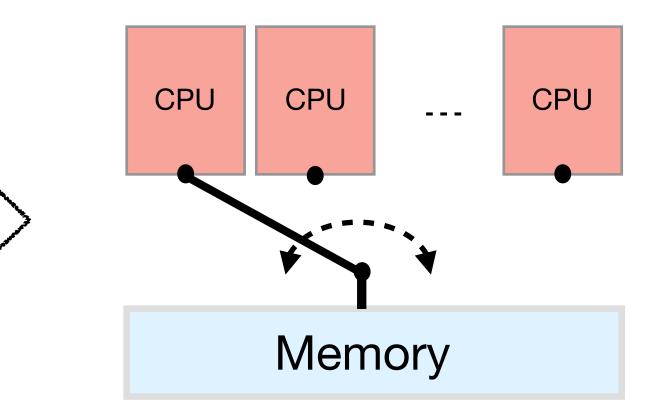

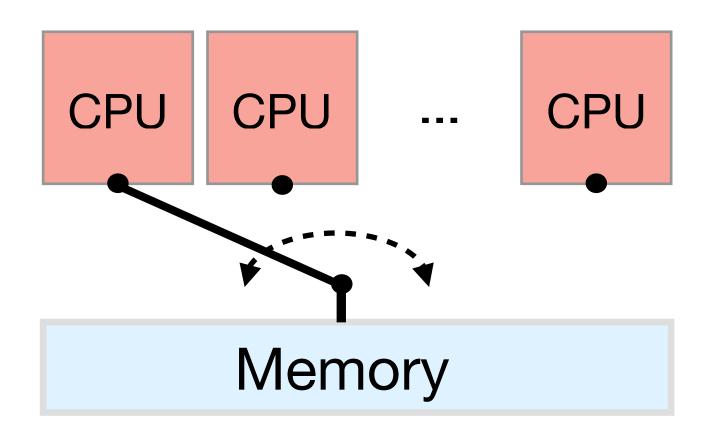

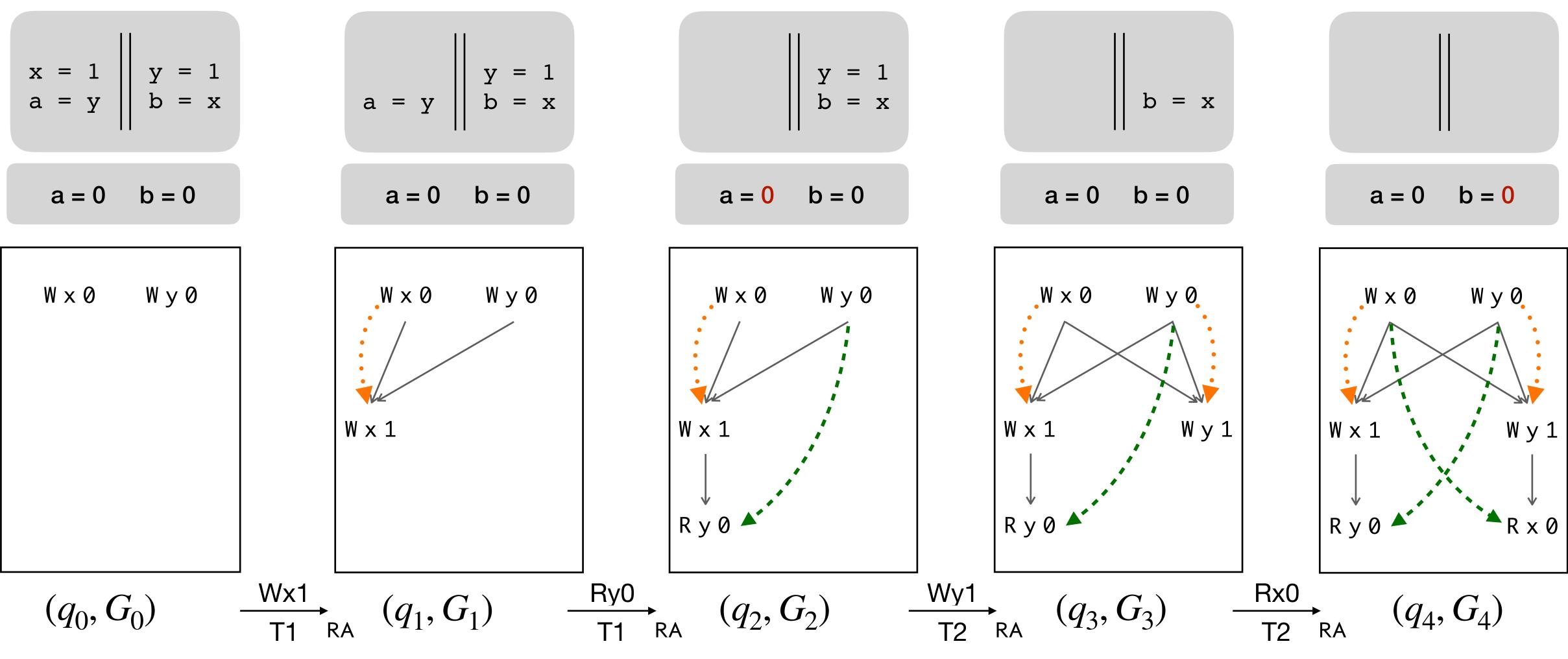

### **Operational version**

### Example: "store-buffer" litmus test

Initial state

final state

**Release**/Acquire

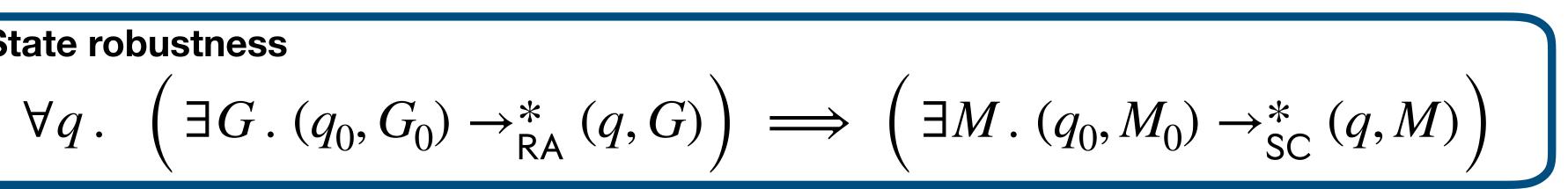

$$\forall q \, \left( \, \exists G \, \left( \, q_0, G_0 \right) \to_{\mathsf{RA}}^* \left( q, G \right) \right)$$

### Bad news...

- Reduction from state reachability [Bouajjani, Derevenetc, Meyer ESOP'13]

• State-reachability for Release/Acquire is undecidable! [Abdulla, Arora, Atig, Krishna PLDI 19]

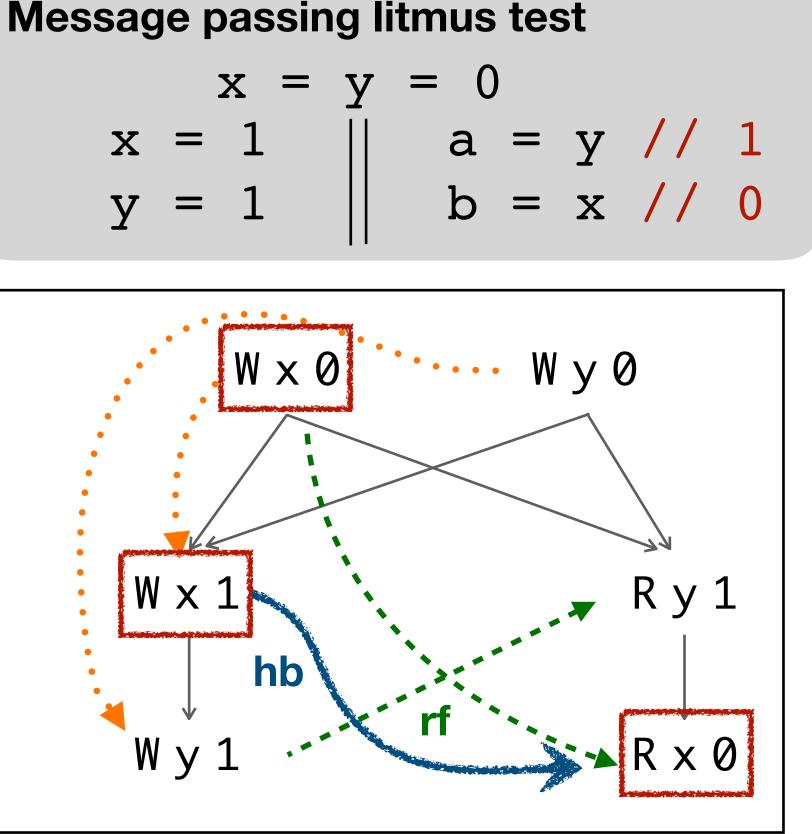

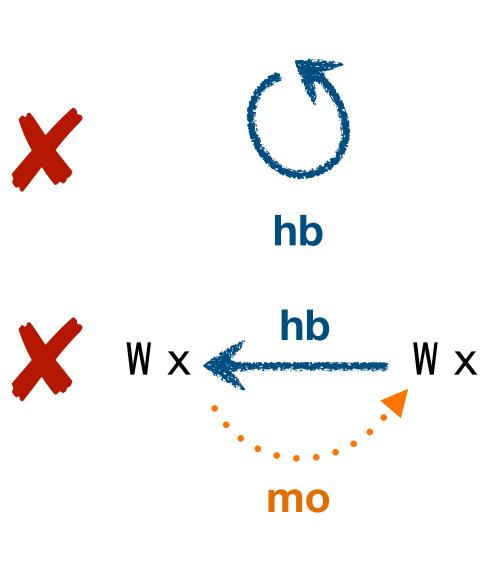

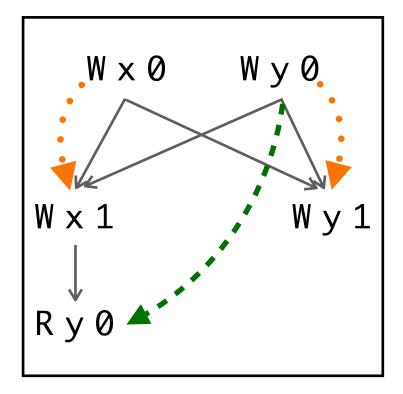

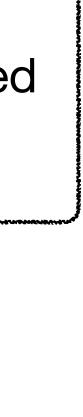

# **Execution-graph robustness hb** $\cup$ **mo** can be linearized to an execution order of an SC-run $\forall q, G \colon (q_0, G_0) \rightarrow_{\mathsf{RA}}^* (q, G) \implies G$ describes an SC-history

**State robustness**

Reduction to *reachability* under *an instrumented* SC semantics allowed by SC disallowed by SC can take an RA-step to a non-SC execution graph robustness  $I_2$  $I_n$ instrumentation

Execution-graph robustness against Release/Acquire is decidable and **PSPACE-complete**. a "minimal" robustness violation:  $(q_0, G_0) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_{n+1}, G_{n+1}) \ll (q_0, G_0) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_{n+1}, G_{n+1}) \ll (q_0, G_0) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_{n+1}, G_{n+1}) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_{n+1}, G_{n+1}) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_n, G_n) \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_1, G_1) \rightarrow_{\mathsf{RA}} (q_1, G_2) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} \dots \rightarrow_{\mathsf{RA}} (q_1, G_2) \rightarrow_{\mathsf{RA}} (q_1, G_2) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} (q_1, G_2) \rightarrow_{\mathsf{RA}} (q_2, G_2) \rightarrow_{\mathsf{RA}} (q_2,$  $(q_0, M_0) \rightarrow_{\mathsf{SC}} (q'_1, M_1) \rightarrow_{\mathsf{SC}} (q'_2, M_2) \rightarrow_{\mathsf{SC}} \dots \rightarrow_{\mathsf{SC}} (q_n, M_n)$  $I_0$

• Every SC-run producing  $G_3$  executes w before the current last event of T2

### Instrumented SC Semantics

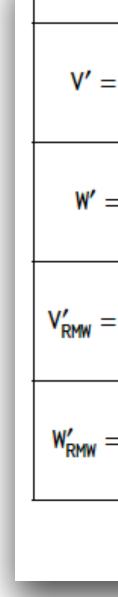

|                           | $\langle \tau, W(x, v) \rangle$ or<br>$\langle \tau, RMW(x, v_{R}, v_{W}) \rangle$                                                 | $\langle \tau, R(x, v) \rangle$                                                                                                |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| $V'_{SC} = \lambda \pi$ . | $\begin{cases} V_{SC}(\tau) \cup M_{SC}(x) & \pi = \tau \\ V_{SC}(\pi) \setminus \{x\} & \pi \neq \tau \end{cases}$                | $\begin{cases} V_{\mathrm{SC}}(\tau) \cup W_{\mathrm{SC}}(x) & \pi = \tau \\ V_{\mathrm{SC}}(\pi) & \pi \neq \tau \end{cases}$ |

| $M'_{SC} = \lambda y.$    | $\begin{cases} M_{\mathrm{SC}}(x) \cup V_{\mathrm{SC}}(\tau) & y = x \\ M_{\mathrm{SC}}(y) \setminus \{x\} & y \neq x \end{cases}$ | $\begin{cases} M_{\mathrm{SC}}(x) \cup V_{\mathrm{SC}}(\tau) & y = x \\ M_{\mathrm{SC}}(y) & y \neq x \end{cases}$             |

| $W'_{SC} = \lambda y.$    | $\begin{cases} M_{\mathrm{SC}}(x) \cup V_{\mathrm{SC}}(\tau) & y = x \\ W_{\mathrm{SC}}(y) \setminus \{x\} & y \neq x \end{cases}$ | $W_{SC}(y)$                                                                                                                    |

Figure 5. Maintaining V<sub>SC</sub>, M<sub>SC</sub> and W<sub>SC</sub> in SCM transitions.

|                     | $\langle \tau, W(x, v) \rangle$ where $v_{R} = M(x)$                                                                                                            | $\langle \tau, R(x, v) \rangle$                                                               | $\langle \tau, RMW(x, v_{R}, v_{W}) \rangle$                                                                                                                          |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $= \lambda \pi, y.$ | $\begin{cases} \emptyset & \pi = \tau, \ y = x \\ \forall(\pi)(x) \cup \{v_{R}\} & \pi \neq \tau, \ y = x \\ \forall(\pi)(y) & y \neq x \end{cases}$            | $\begin{cases} V(\tau)(y) \cap W(x)(y) & \pi = \tau \\ V(\pi)(y) & \pi \neq \tau \end{cases}$ | $\begin{cases} V(\tau)(y) \cap W(x)(y) & \pi = \tau \\ V(\pi)(x) \cup \{\upsilon_{R}\} & \pi \neq \tau, \ y = z \\ V(\pi)(y) & \pi \neq \tau, \ y \neq z \end{cases}$ |

| $= \lambda z, y.$   | $\begin{cases} V(\tau)(y) & z = x, \ y \neq x \\ W(z)(x) \cup \{\upsilon_{R}\} & z \neq x, \ y = x \\ W(z)(y) & \text{otherwise} \end{cases}$                   | W(z)(y)                                                                                       | $\begin{cases} W(x)(y) \cap V(\tau)(y) & z = x, \ y \neq x \\ W(z)(x) \cup \{\upsilon_{R}\} & z \neq x, \ y = x \\ W(z)(y) & \text{otherwise} \end{cases}$            |

| $= \lambda \pi, y.$ | $\begin{cases} \emptyset & \pi = \tau, \ y = x \\ V_{RMW}(\pi)(x) \cup \{\upsilon_{R}\} & \pi \neq \tau, \ y = x \\ V_{RMW}(\pi)(y) & y \neq x \end{cases}$     | $\begin{cases} V_{\rm RMW}(\tau)(y) \\ V_{\rm RMW}(\pi)(y) \end{cases}$                       | $y) \cap W_{RMW}(x)(y)  \pi = \tau$ $y) \qquad \pi \neq \tau$                                                                                                         |

| $= \lambda z, y.$   | $\begin{cases} V_{RMW}(\tau)(y) & z = x, \ y \neq x \\ W_{RMW}(z)(x) \cup \{\upsilon_{R}\} & z \neq x, \ y = x \\ W_{RMW}(z)(y) & \text{otherwise} \end{cases}$ | $W_{RMW}(z)(y)$                                                                               | $\begin{cases} W_{RMW}(x)(y) \cap V_{RMW}(\tau)(y) & z = x, \\ W_{RMW}(z)(y) & \text{otherw} \end{cases}$                                                             |

Figure 6. Maintaining V, W, V<sub>RMW</sub>, and W<sub>RMW</sub> in SCM transitions.

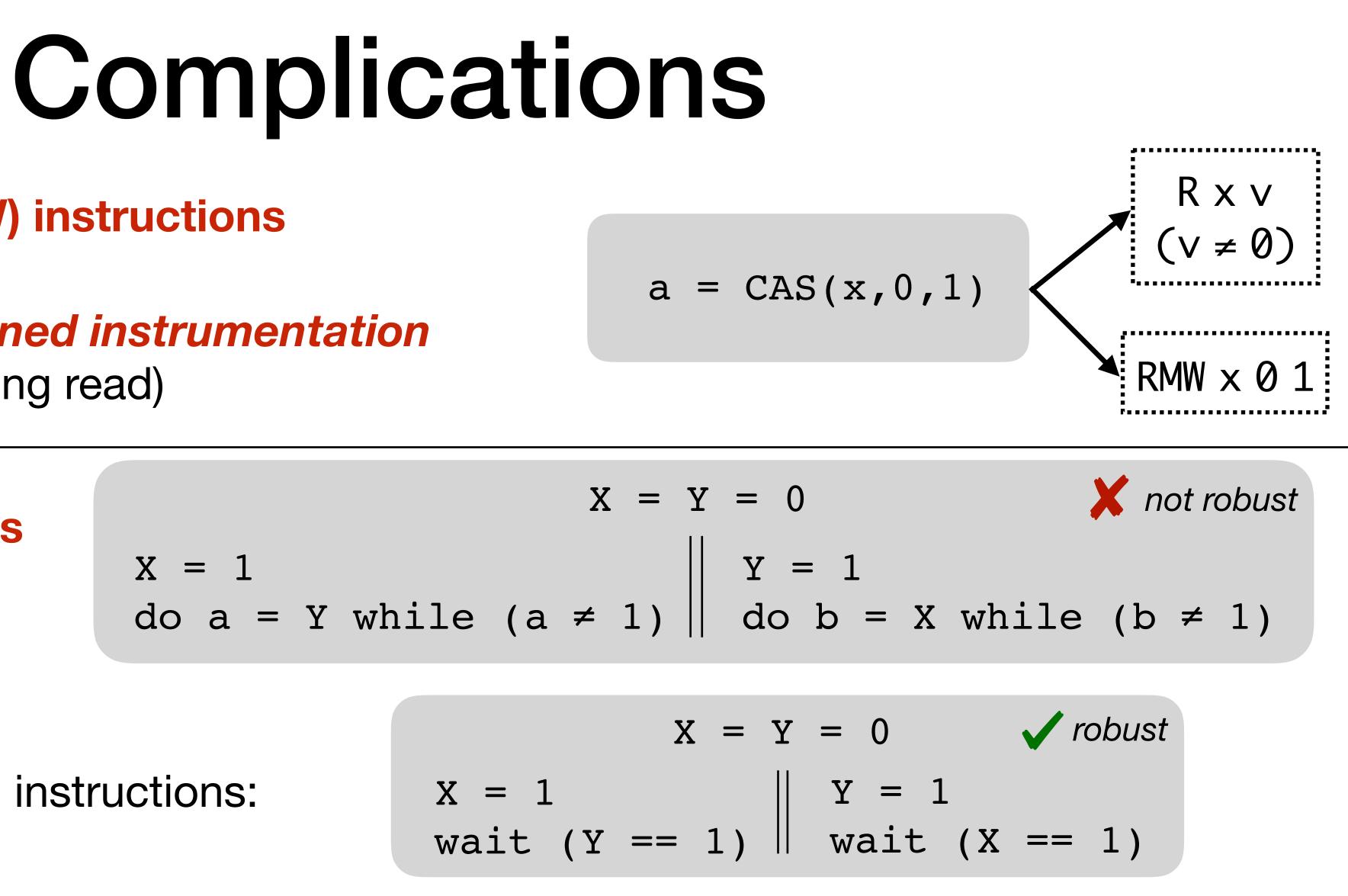

Read-modify-write (RMW) instructions

require much more *refined instrumentation* (depends on values being read)

Masking benign violations

masked using blocking instructions:

• Sequentially consistent fences

modelled as RMWs

| Evaluation           |            |                    |                      |            |       |                        |            |                                        |

|----------------------|------------|--------------------|----------------------|------------|-------|------------------------|------------|----------------------------------------|

| number of<br>threads |            | number<br>of lines | robust?              |            | 1     | obustness<br>mentation |            | robustness<br>against x86-TSO          |

|                      |            |                    |                      | <b>T</b> : | SC    | Trenche                | er (TSO)   |                                        |

|                      | # <b>T</b> | LoC                | Result               | Time (sec) | (sec) | Result                 | Time (sec) | )                                      |

| spin-lock            | 2          | 34                 | <ul> <li></li> </ul> | 1.6        | 1.2   | <ul> <li></li> </ul>   | 5.4        |                                        |

| seq-lock             | 4          | 49                 | <ul> <li></li> </ul> | 20.7       | 3.4   | ✓                      | 8.9        |                                        |

| Peterson             | 2          | 28                 | X                    | 2.5        | 1.2   | ×                      | 5.6        |                                        |

| Peterson for x86-TSO | 2          | 30                 | X                    | 3.3        | 1.3   | $\checkmark$           | 5.6        |                                        |

| Peterson - Dmitriy   | 2          | 36                 |                      | 4.3        | 1.2   | $\checkmark$           | 5.5        |                                        |

| Peterson - Bartosz   | 2          | 28                 | X                    | 3.4        | 1.1   | X                      | 5.6        | _~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

| RCU                  | 4          | 74                 |                      | 67.6       | 2.2   | <b>X</b> *             | -          | requires                               |

| RCU (offline)        | 3          | 215                |                      | 137.9      | 18.3  | × *                    | -          | instructions                           |

# Summary

- We developed a sound and precise reduction from execution-graph robustness against Release/Acquire semantics to a reachability problem under SC.

- Execution-graph robustness against Release/Acquire is PSPACE-complete.

- We **implemented** the reduction and verified several challenging algorithms, demonstrating in particular that execution-graph robustness is not overly strong.

| verification |   | verifi |

|--------------|---|--------|

| under        | = | S      |

| weak memory  |   | CC     |

Thank you!

| state<br>robustness | execution<br>graph<br>robustness |

|---------------------|----------------------------------|

|                     |                                  |

|                     |                                  |